新品发布 | EsseCDC:攻克跨时钟域亚稳态风险的国产验证引擎

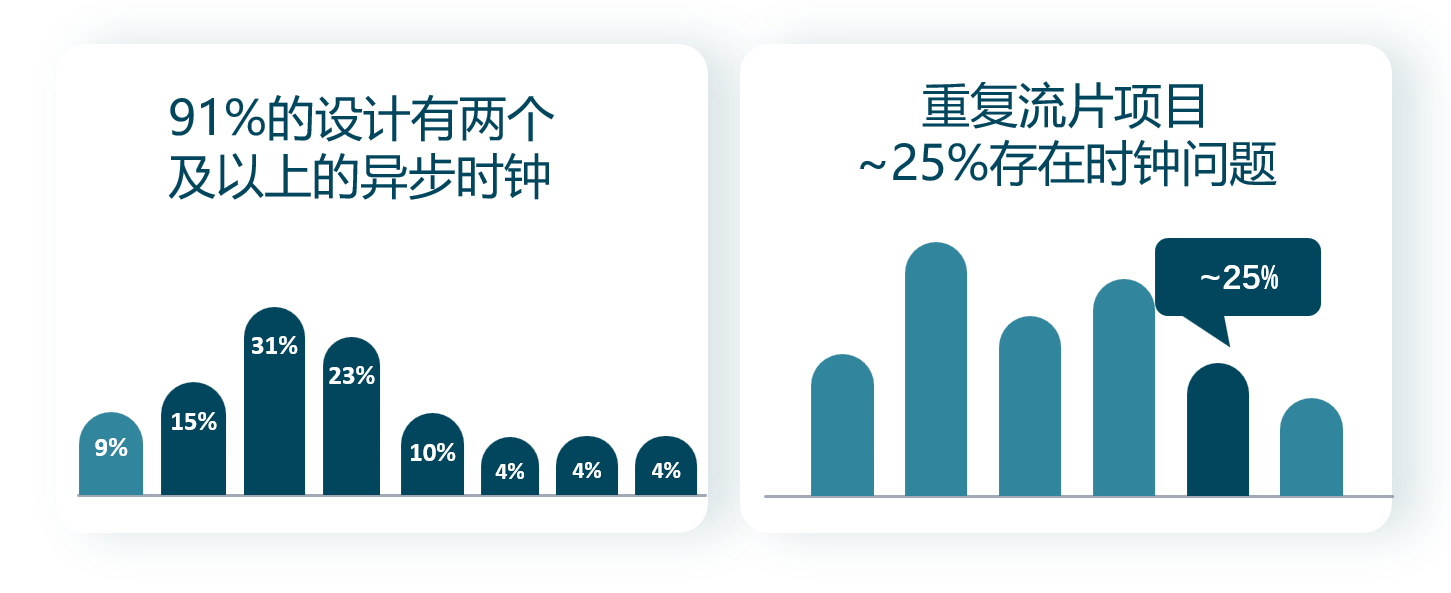

在异构集成的芯片设计中,跨时钟域信号传输引发的亚稳态问题已成为流片失败的核心诱因。据EDA行业相关权威报告指出,现代SoC设计中91%的芯片需协调两个及以上异步时钟域,而近25%的流片失败案例直接源于跨时钟域路径缺陷。随着AI大算力芯片的演进,千级时钟域网络与定制化同步器的复杂性,使得传统检查工具面临漏检率攀升、误报率居高不下的技术瓶颈。

From: Siemens EDA 2020 Wilson Research Group functional verification study

国微芯正式推出首款芯天成®形式验证平台跨时钟域检查工具——EsseCDC。该产品以动态时钟传播算法破除时钟域规模壁垒,通过时序元件反向推导自动构建完整时钟传播路径;借力同步器语义解析引擎解构多级同步链与定制化结构(如脉冲FIFO的使能路径约束、异步握手的请求-响应时序);并运用形式化亚稳态检测模型,突破传统静态分析与仿真的局限,动态捕获并精确分析时钟域同步中的亚稳态风险。

痛点锁定:三大跨时钟域验证危机

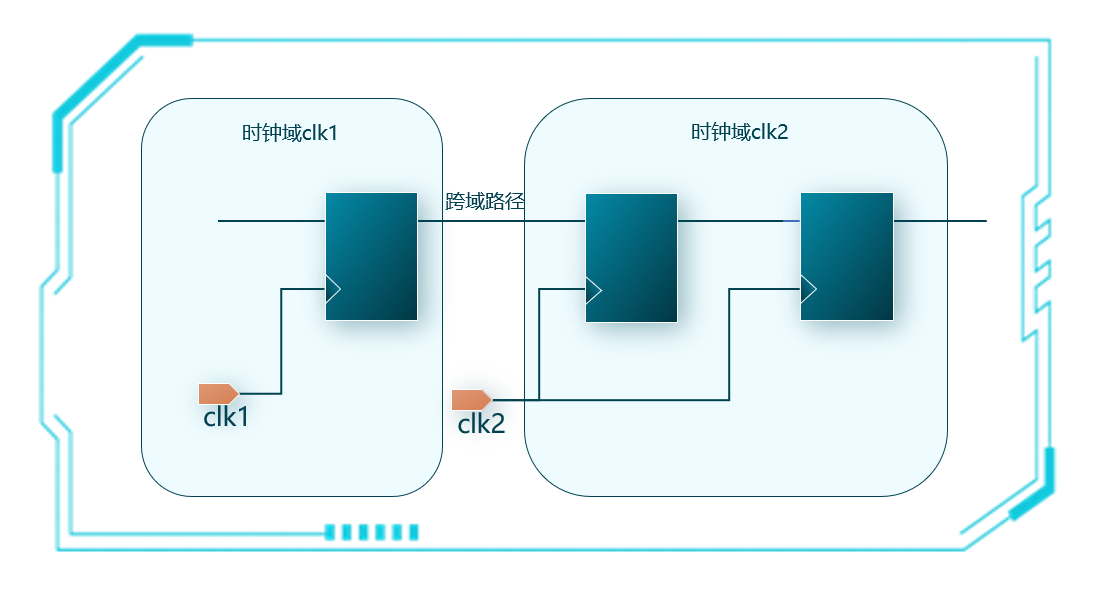

现代芯片设计正面临三大跨时钟域验证危机:

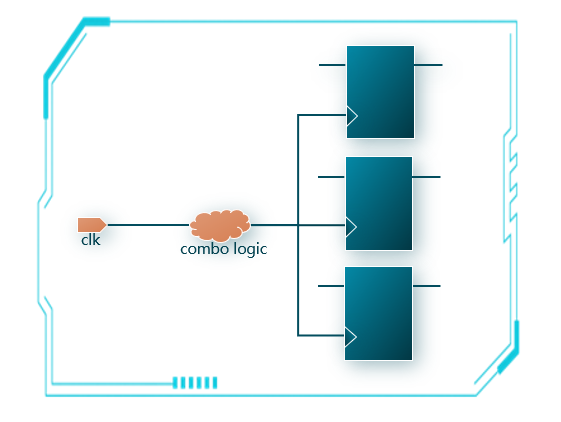

域规模失控:复杂芯片中异步时钟域已成为普遍存在,但传统工具难以充分管理时钟路径,导致关键路径遗漏风险高;

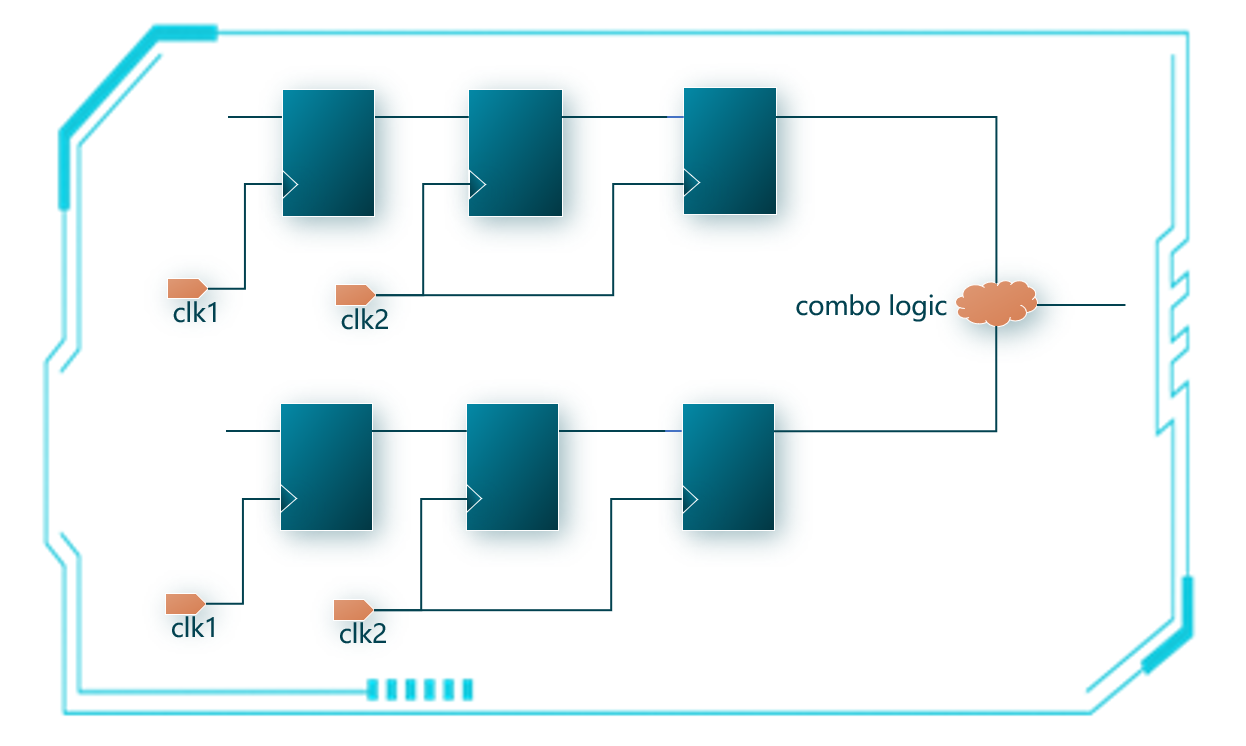

同步器深度危机:日益复杂的同步结构显著增加了验证误报率,增加了工程辨别成本;

定制结构失效:脉冲FIFO/异步握手等动态语义约束超规则库覆盖。

三者叠加,极大推升流片失败率,跨时钟域信号如同精密齿轮中的“关键齿牙”,毫厘之失足以崩坏全局时序。

破局之道:三阶技术引擎重构跨域验证范式

技术研新——算法突破传统能力边界

1.智能时钟传播引擎:自动化识别,确保时钟域完整性与规则覆盖全面性

传统局限:依赖人工编写SDC约束,多衍生时钟(如分频器、门控时钟)易漏检,规则覆盖不全。

国微芯EsseCDC技术突破:

动态拓扑追踪:专有独特算法自动反向追踪FF/Latch时钟源,精准识别create_generated_clock场景,大幅降低时钟遗漏风险(规则全面);

冲突智能校验:实时检测用户定义约束与推断结果的矛盾;

核心功能支撑:全面兼容不同版本SDC、SGDC约束语法,并实现自动推断时钟域的CDC检查,从根源提升检查完整性。

2. 深度同步器识别引擎:精准解析结构,消除误报盲区,提升报告精准度

传统局限:规则库僵化(仅匹配双触发器),对复杂同步器(握手协议/FIFO)误报率较高,报告噪音大。

国微芯EsseCDC技术突破:

动态语义解析:专有独特算法深度分析控制信号与数据路径时序逻辑,灵活支持用户自定义同步深度,精准适配各类同步方案,显著降低误报;

跨层级协同验证:洞察局部同步器与全局时钟路径的交互,彻底杜绝“局部正确、全局失效”的验证盲区;

核心功能支撑:支持对report降噪处理,智能忽略不关心的违例,让工程师聚焦真实问题,支持RTL和Netlist阶段的CDC检查,灵活覆盖设计流程。

3. 亚稳态融合验证引擎:超越静态分析,捕获动态风险,实现高效深度验证

传统局限:静态代码分析无法捕获路径延迟偏移,收敛问题漏检率高,深度不足效率低。

国微芯EsseCDC技术突破:

时钟发散风险捕获:量化评估组合路径延迟偏移,可配置阈值检查发散路径的亚稳态传播风险;

形式化增强验证:高效注入亚稳态模型,自动化验证格雷码等同步机制的正确性,覆盖传统仿真难以触发的深层场景;

核心功能支撑:结合RTL/Netlist检查能力,动态追踪跨时钟域毛刺生成路径。

【操作流程DEMO演示】

应用场景——从复杂架构到定制协议的全面防护

1.基础场景:全自动CDC验证闭环

EsseCDC通过时钟传播自重构引擎实现千级时钟域规模的零遗漏检查,具备一键定位异步时钟重叠路径与智能降噪聚焦致命违例的核心能力,有效支撑高性能芯片的跨时钟域Glitch风险检测及多时钟域数据完整性验证。

2.高阶场景:CDC+RDC双域联防体系

协同价值 | 技术实现 | 用户收益 |

时钟-复位耦合验证 | 联合检测复位信号对跨时钟路径的干扰 | 避免异步复位引发的连锁反应 |

统一调试环境 | CDC与RDC违例合并分析,路径可交叉追溯 | 有效减少上下文切换时间 |

3.定制场景:复杂同步架构专项验证

突破传统工具局限,基于同步器语义解析引擎实现脉冲FIFO使能窗口约束识别与异步握手协议建模,并通过开放API集成企业级私有同步策略,为国产大算力芯片定制握手协议及低功耗芯片门控时钟提供专项验证保障。

生态赋能——国产工艺深度适配

1.国产工艺库兼

主流先进节点适配:针对主流先进工艺节点的时序特性进行深度优化,提供定制化的同步器检测方案;

国产定制结构强支持:对国内特有的定制化同步结构,实现高检出率与极低误报率。

2.国产工具链协

广泛集成主流平台:无缝对接主流综合平台,自动解析网表拓扑信息;

深度兼容核心工艺约束:融合一线代工厂关键工艺约束库,全面支持核心工艺参数。

协同谋新:千域万径间的国产验证之力

国微芯营销中心总经理邓金斌:“面对千域异构集成带来的算力挑战,EsseCDC通过创新的拓扑重构算法重塑时钟架构——大幅降低时钟遗漏风险,并运用先进的亚稳态传播模型量化海量路径风险。历经先进工艺实践验证的EsseCDC,其高可靠性为客户的芯片设计提供了坚实保障。依托国产EDA生态协同优势,EsseCDC 积极响应客户的本土化需求——不仅灵活兼容客户采用的国内自主工艺特性,更能按需定制客户专属的企业级验证规则,为国内芯片设计、Fab厂等客户提供强力支撑。”

一微-芯片研发总监 何再生:“EsseCDC在跨时钟域检查方面展现了令人信赖的能力,帮助我们高效定位设计中的时序风险,大大增强了芯片运行的稳定性和可靠性。尤其让我们印象深刻的是,该工具及时预防规避了某款SOC芯片时钟树功能缺失的风险,最终为整个验证周期与产品的成功上市节省了大量时间。”

EsseCDC以三大创新引擎突破跨时钟域验证瓶颈,有效化解域规模失控与同步器危机,显著提升芯片的时序安全可靠性。未来,依托国产工艺生态协同与定制化扩展,EsseCDC将持续赋能半导体产业,从基础Glitch检查到高阶双域联防体系,推动行业向“零风险流片”愿景迈进,国微芯也将持续助力国产芯片在算力竞赛中实现从“跟跑”到“领跑”的跨越式崛起。