新品发布 | EsseLint:从源头拦截设计漏洞的语法检查引擎

随着数字设计领域迅速发展,Verilog/VHDL等硬件描述语言(HDL)已成为电子电路设计验证的关键载体。设计师与验证工程师面临日益复杂的设计挑战:亟需在早期阶段发现语法错误、潜在设计问题及代码规范违规。设计团队因编码标准差异,迫切要求工具可按项目灵活配置检查策略。随着行业规模扩张,市场对高效国产HDL Lint工具的需求持续攀升。

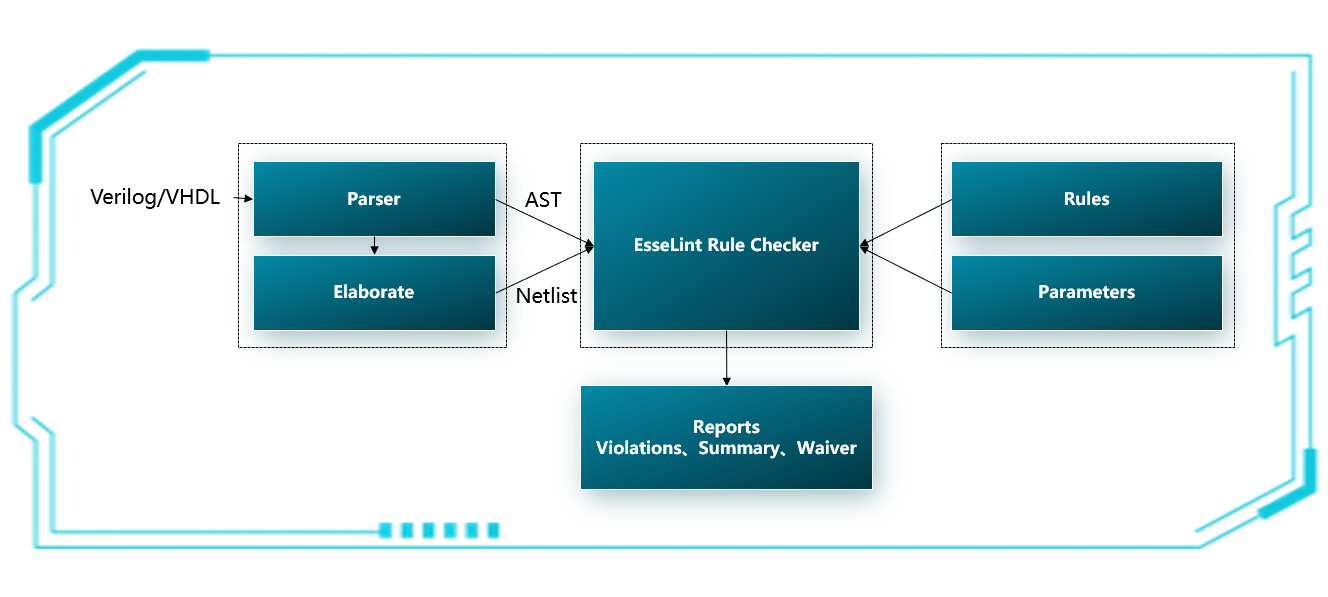

国微芯正式推出芯天成®形式验证平台设计规则检查工具——EsseLint,精准响应行业诉求。该产品通过深度扫描代码风格、语法规范、可综合性及电路结构问题,系统性规避因设计风格不一致、不合理电路结构和仿真综合差异引发的潜在风险,显著提升代码质量与可维护性,为芯片设计功能正确性和稳定性构筑强支撑基座。

痛点锁定:百万门级设计质量管控三重失效风险

芯片复杂度激增令Verilog/VHDL设计深陷质量困局:

规模激增引爆设计风险:百万门级复杂度下,语法错误、编码规范混乱及不可综合代码频发,显著增加综合流程中断风险与后期调试成本。

质量隐患直传导流片风险:仿真与综合结果不匹配、电路结构缺陷等隐患因检测缺失,直接推升流片失败概率。

传统工具国产化适配不足:现有方案对140万Cell设计检测耗时数分钟级,且规则僵化难满足本土定制需求,制约迭代效率。

——效率瓶颈、灵活性缺失与国产化适配不足,构成当前质量管控的核心短板之一。

破局之道:四大功能引擎重构质量防线

技术研新——全栈式规则验证引擎

1. 智能规则矩阵

► 当前构建数百加原子级规则库,完整涵盖:

语法检查层:实时解析Verilog/SV/VHDL语法树,精准拦截端口未连接、信号多重定义等基础错误;

规范检查层:强制统一命名规范(如模块名前缀_信号驼峰法)与代码风格,消除团队协作歧义;

电路结构层:深度检测组合逻辑环、锁存器隐式推断、时序路径冲突等硬件风险,预防硅前设计返工。

► 支持动态规则扩展,用户可注入定制规则(如CPU特有复位策略检查),国产化规则可定制化适配。

2. 超高效验证架构

► 百倍级加速:实测案例中140万Cell设计扫描仅需129秒,较传统工具效率显著提升;

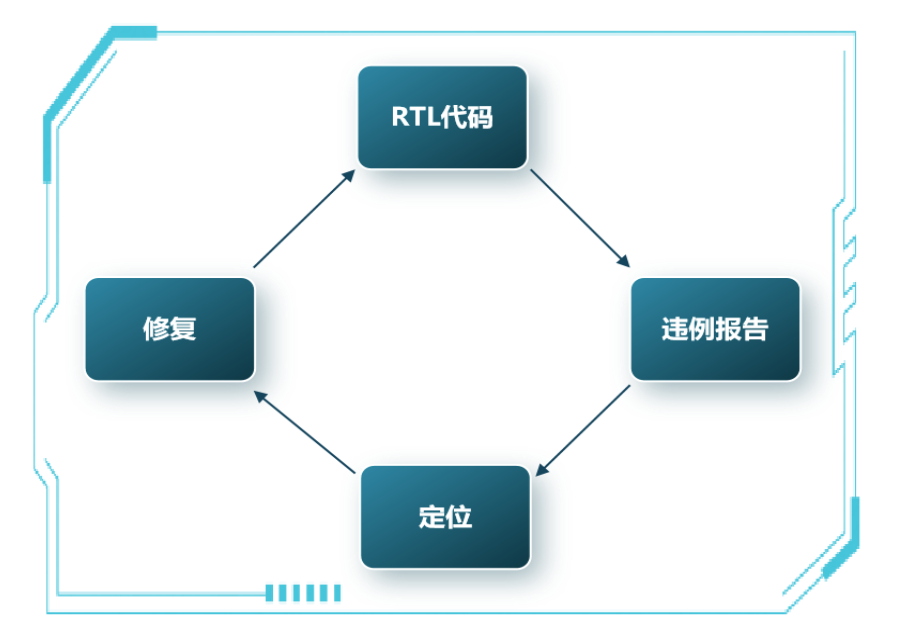

3. 深度诊断报告系统

► 生成四级错误追踪链路:

违例类型——错误代码行——修复建议——waive违例信息

► waive违例信息,支持违例信息豁免,避免重复确认报错信息;

► 集成可视化调试沙盒,支持错误代码段实时修改验证,问题定位效率精准提升。

4. 标准化流程集成

► 预置十数条自动化TCL命令集

主要操作链:read_design -> select_goal -> rule_check -> report_gen

应用场景:全流程风险拦截体系

1. 设计阶段快速检测设计语法问题

通过实时语法检查拦截未声明变量等基础错误,预防综合流程崩溃。

2. 验证阶段识别潜在的电路结构问题

深度扫描多驱动冲突、锁存器推断等电路缺陷,消除仿真综合断层风险。

3. 验证阶段评估代码的质量

输出量化评分报告,驱动可读性与可维护性优化。

4. 辅助并加快完成验证sign-off

TCL自动化流程压缩50%签收周期。

5. 适用于CPU/GPU/ASIC芯片的语法检查

预置芯片专用规则包,全面支持国产CPU/GPU开发全流程语法护航。支持国产架构扩展。

生态赋能:共建国产EDA可持续发展体系

1. 标准筑基:开源协议与IEEE标准深度互

语法标准对齐:支持IEEE 1800(SystemVerilog)/ 1076(VHDL)语法标准,实现国际验证流程无缝迁移;

预制模板:预置国产CPU/GPU/ASIC等芯片设计规范检查模板,降低本土企业技术迁移门槛。

2. 产业协同:国产芯片全栈适配生

架构支持:深度适配主流国产CPU架构设计规范,预置存储芯片时序检查等专用规则包;

工具链集成:补齐国微芯形式验证平台EsseFormal,贯穿于数字IC设计的各个阶段,综合工具共建验证闭环,为芯片设计过程中的每个环节提供验证解决方案,兼具定制化和集成化两大优势,能够精准满足客户需求。

协同谋新:突破传统工具效率与国产化瓶颈

国微芯营销中心总经理邓金斌:“通过构建自主知识产权的核心技术体系,国微芯为国产芯片提供了高可靠性代码质量保障基座,并推动形式验证、综合优化等技术的协同发展。EsseLint将有效赋能本土芯片企业,强化国产EDA产业链韧性。未来国微芯将持续深化形式验证等核心技术,协同推动综合优化等方向创新。在生态上,联合产业链伙伴共建开放共赢的EDA工具链,助力中国芯片产业实现全面自主化!”

正和微芯-芯片设计总监 张庆:“EsseLint在超大规模芯片设计中展现出变革性价值。其深度规则引擎显著提升代码规范性,极大解决团队协作中的风格碎片化问题;高速解析能力将设计隐患识别效率提升至行业新高度,帮助我们系统性规避流片风险。工具创新的TCL自动化流程已成为设计验证不可或缺的质量基座。”

EsseLint以智能规则矩阵、超高效验证架构、深度诊断报告和标准化流程四大功能,精准拦截语法错误与电路结构隐患,更以百倍级加速突破传统效率瓶颈,为芯片筑牢代码质量基座。其深度国产化适配能力,支持动态规则扩展与自动化流程集成,显著压缩验证签收周期。随着生态协同深化,EsseLint将持续赋能设计源头风险拦截,驱动国产EDA工具链自主创新,助力中国芯片产业构建"设计即正确"的高质量研发范式。