芯天成可靠性平台EsseChar

EsseChar

EsseSIM

EsseSanity

EsseTime

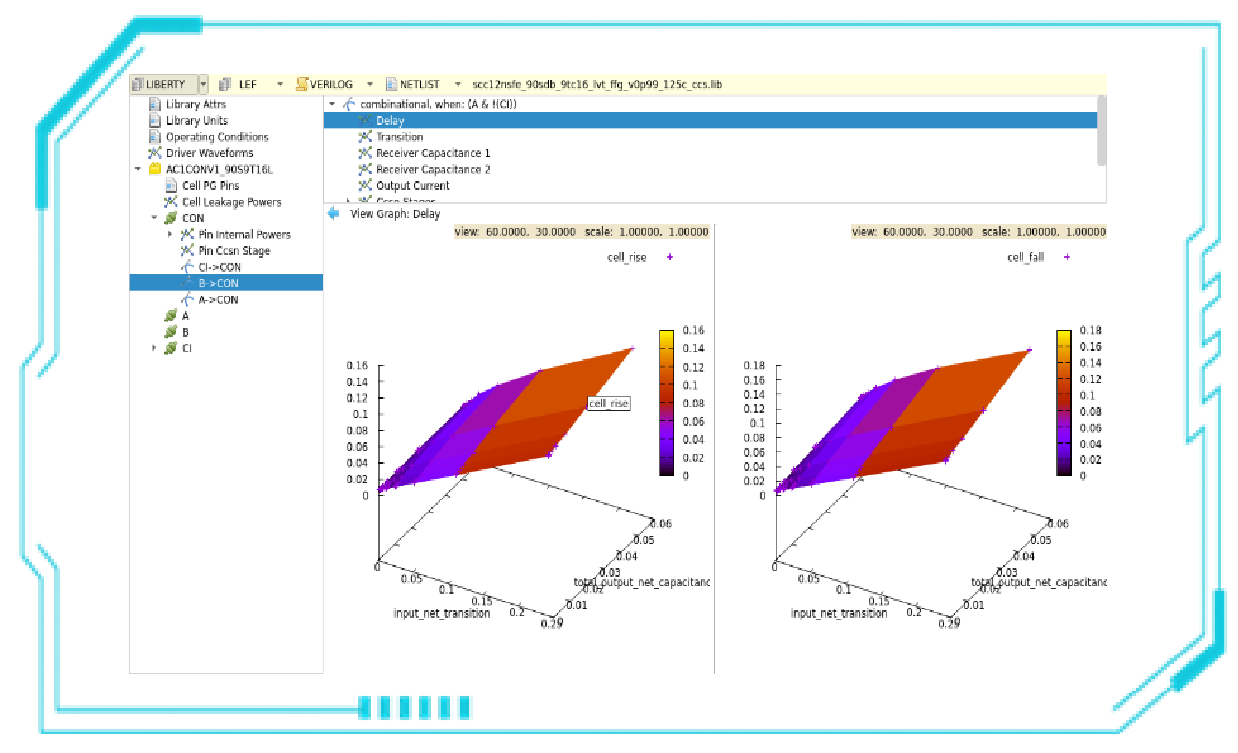

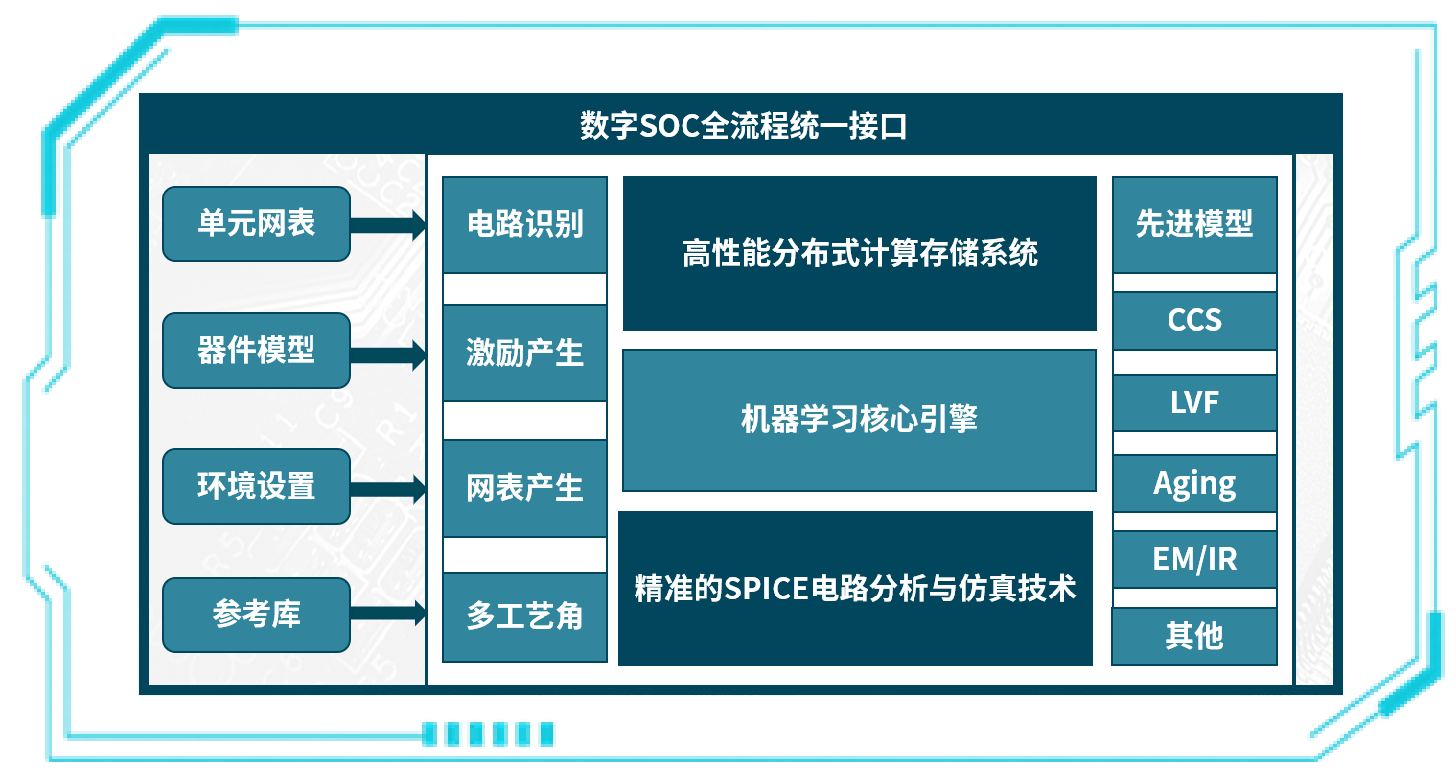

产品简介

芯天成特征化提取工具EsseChar,是国微芯自主开发的新一代特征化工具,基于自主高效的负载均衡分布式系统,内嵌高速仿真软件、机器学习引擎,能快速抽取客户在先进工艺节点所需要的先进模型(包括不同PVT下CCS、LVF、Aging等模型),SoC设计平台一体化设计,能够快速简便地实现单元库特征化需求,并无缝反馈到时序分析平台、功耗分析平台、可靠性设计平台等,真正实现数字全流程一体化。

核心优势

快速蒙特卡罗LVF单元建库;

业界领先的老化库建模功能;

高效率负载平衡分布式平台;

最差时序工作条件自动选取;

支持先进工艺时序签核精度。

产品功能

支持NLDM、NLPM、CCS、LVF等多种模型;

支持快速蒙特卡洛仿真LVF建库;

先进机器学习算法帮助快速收敛;

支持标准单元、接口单元及各种定制单元;

模型精度符合签核标准。

应用方案

数字设计基础单元库开发;

晶圆厂设计服务部门PDK套件;

Fabless厂商定制单元建库;

SoC开发中的多工艺角ReChar。

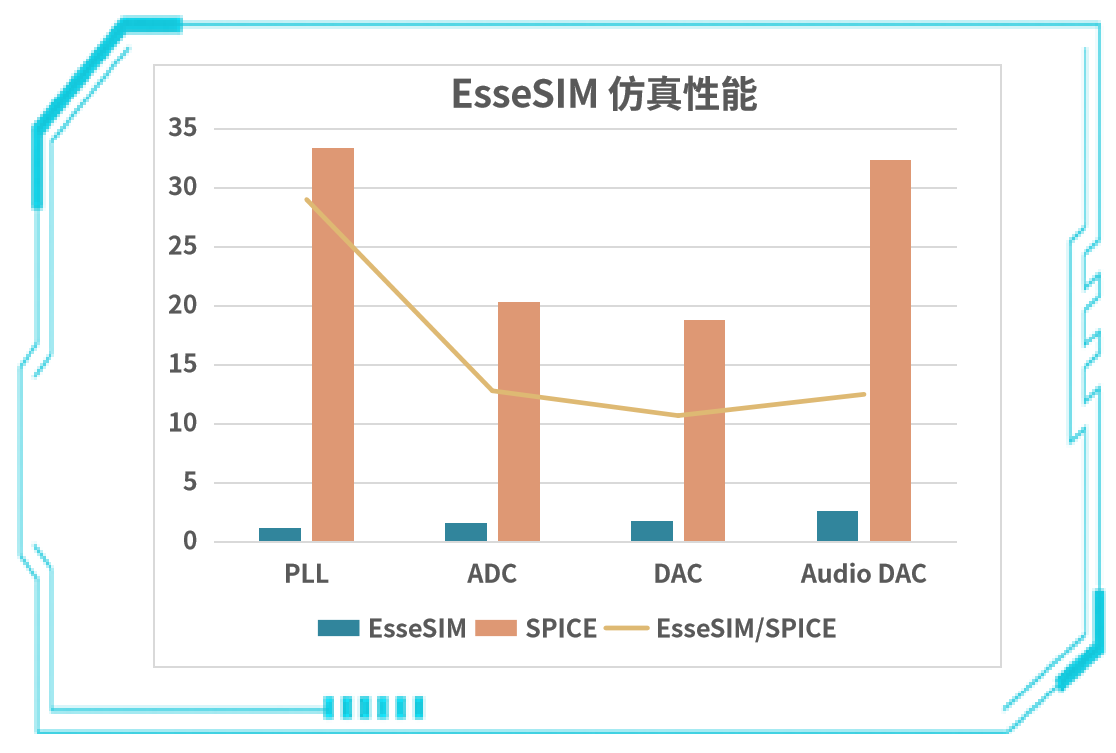

产品简介

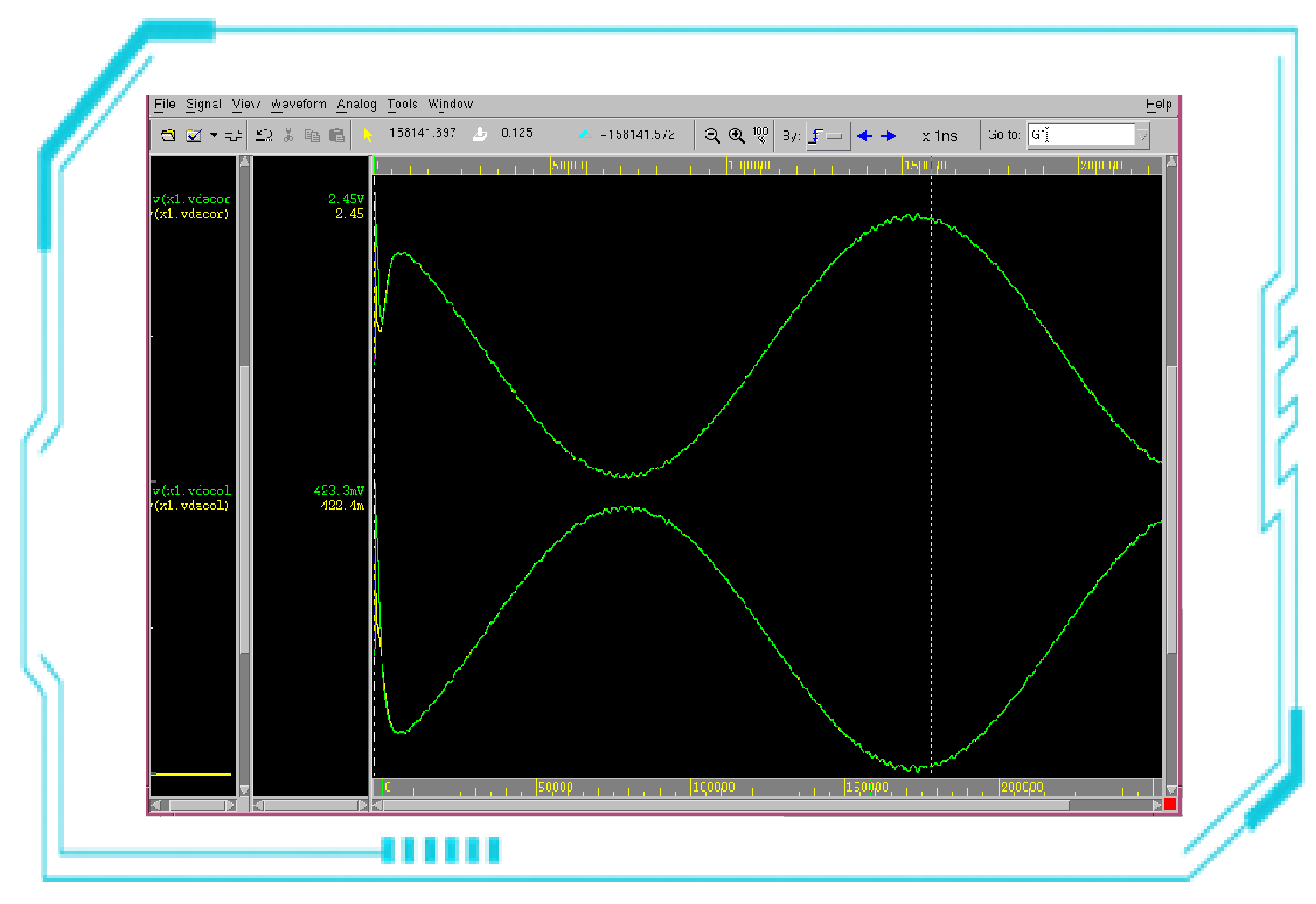

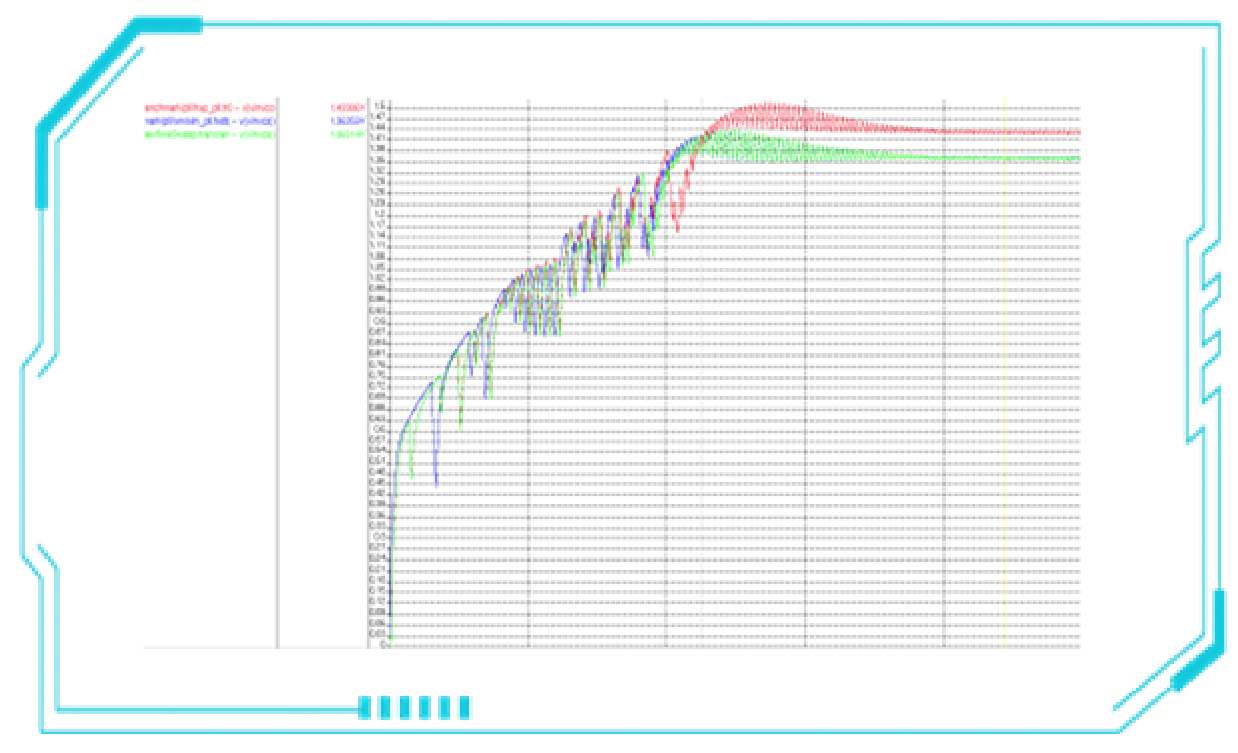

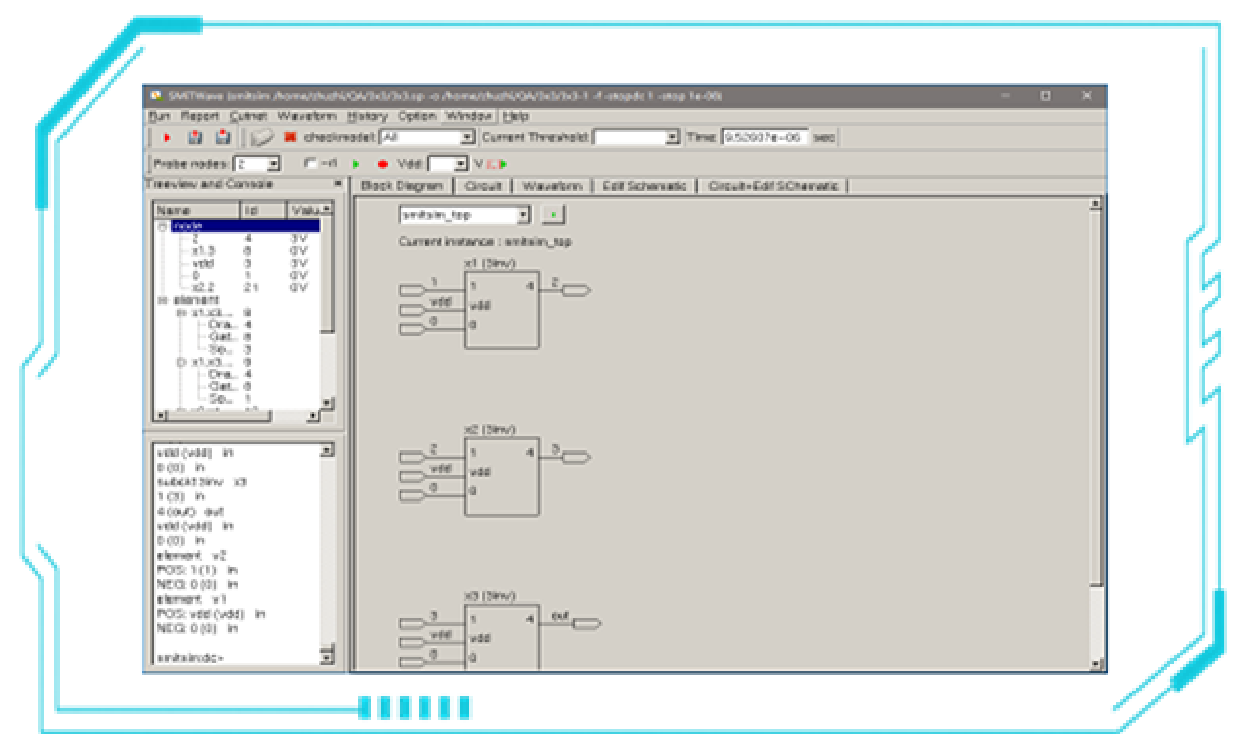

芯天成并行电路仿真工具EsseSIM,是国微芯自主研发的新一代SPICE高精度、高性能、大容量电路仿真工具,可应对高度集成的多功能电路设计仿真需要,如post-layout仿真、电路可靠性仿真等,为模拟电路设计、电路单元特征化、混合电路和数字电路模块验证等提供更好的仿真解决方案。

该产品基于分层次存储和电路分割并行引擎架构,集成SPICE仿真技术、高性能仿真技术、多线程和分布式并行计算技术以及交互式仿真技术,支持业界标准SPICE模型和Verilog-A模型,同时兼容商业SPICE输入输出文件,为成熟和先进技术节点电路设计提供可靠的SPICE精度电路仿真,且随着计算资源的增加,仿真速度也会相应提升。配备了电路图输入图形界面和高性能信号波形显示工具,并提供了一个集成的电路调试环境,帮助快速查找解决电路仿真问题。

核心优势

提供电路分层存储及分割并行计算引擎;

支持众多MOS/DIODE/BJT器件电路模型;

支持用户自定义模型或者VerilogA模型;

支持晶体管老化引起的电路可靠性仿真;

支持多线程多CPU及分布式并行仿真;

集成交互式仿真及信号波形显示调试功能。

产品功能

支持多种仿真分析如TRAN、DC、AC、Noise、TranNoise等;

支持多种参数变化模式如Linear、Monte-Carlo、Bisection等;

支持晶体管老化引起的电路可靠性仿真分析;

支持并行加速仿真,可多核/CPU,多节点,云平台部署;

支持成熟和先进技术节点标准SPICE模型;

支持用户自定义SPICE模型或者自定义Verilog-A模型;

兼容Hspice和Spectre输入文件,多种输出文件;

支持多种波形文件输出格式以及众多测量语句;

支持任意时间点交互式瞬态仿真、增量仿真;

配置电路图输入及信号波形显示GUI。

应用方案

模拟电路设计和验证仿真;

数字电路单元特征化仿真;

晶体管老化可靠性设计仿真。

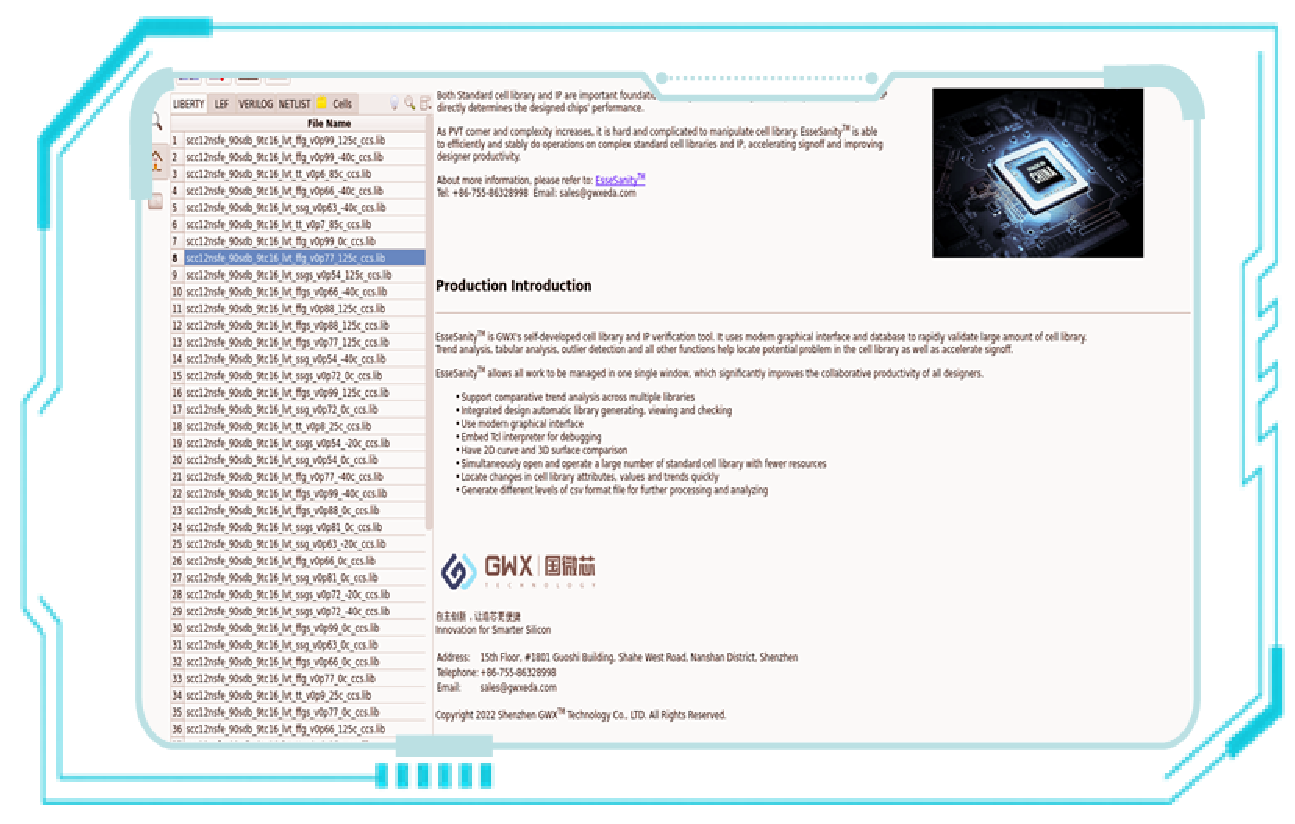

产品简介

芯天成单元库正确性检查工具EsseSanity,是国微芯自主开发的综合性IP数据分析管理应用平台,采用现代图形界面以及数据库技术,能快速分析管理验证海量单元库。质量检查、趋势分析、表格分析、异常点检测等功能可以快速定位单元库的潜在问题,帮助加速签核。IP数据管理能够对数据进行解析,并按文件类型进行分类,同时提供关键信息的快速查看功能,帮助用户掌握IP数据的整体情况。单元库建库一体化设计、单元库的对比检查以及IP数据管理等功能,能够在同一个窗口管理所有工作,大大提高建库人员和设计人员的协同工作效率。

核心优势

图形界面多PVT一键式建库;

支持多个库的PPA对比分析;

内嵌Tcl解释器便于调试;

IP数据解析速度快,且占用资源少;

IP库验证RUNSET脚本智能化构建。

![]()

产品功能

单元库的结构化查看;

单元库多角度质量检查;

单元库多角度质量检查;

DRC、LVS批量运行;

IP数据综合分析管理。

应用方案

单元库签核前检查;

多PVT质量分析;

设计套件可靠性检查;

Liberty大数据分析;

IP数据综合管理查看。

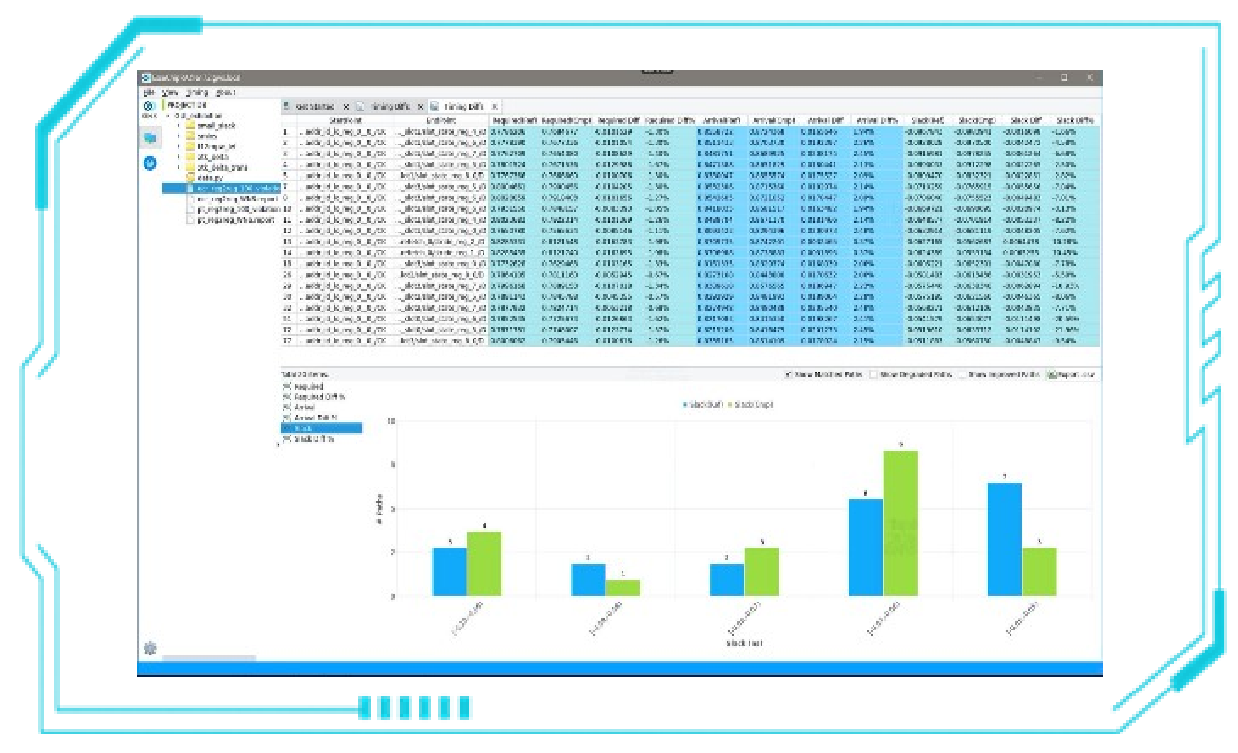

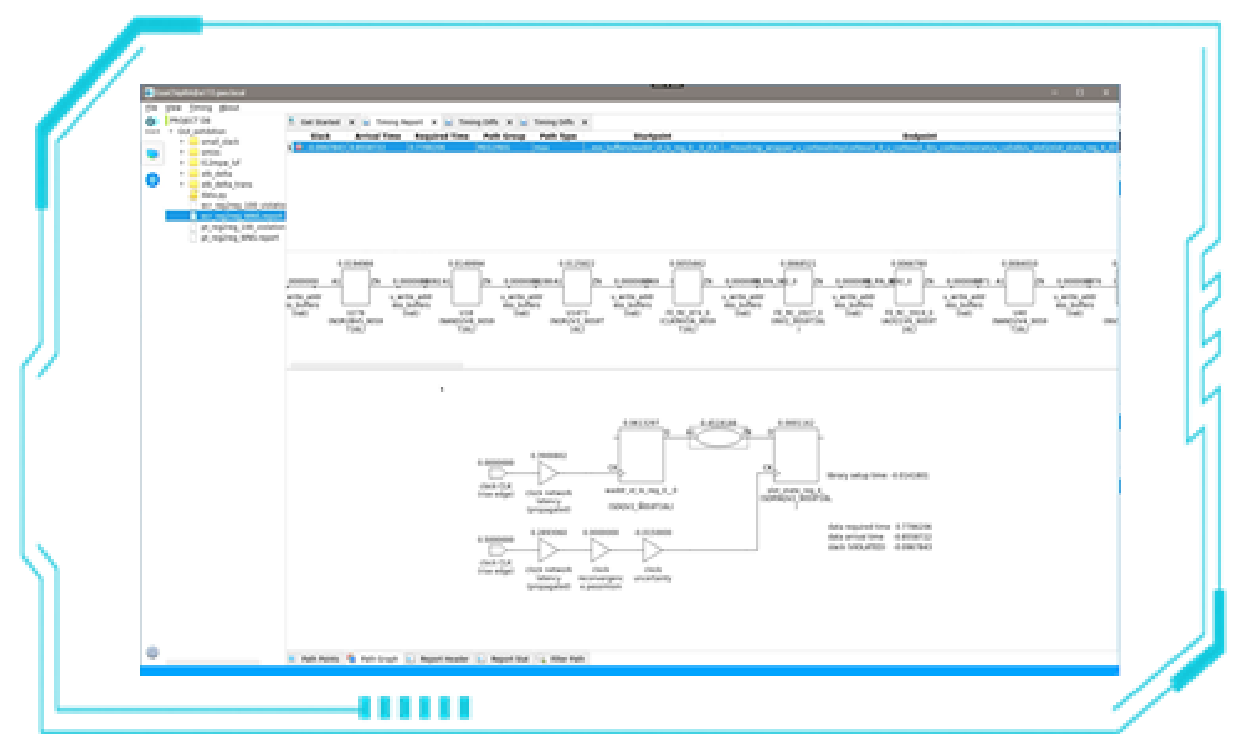

产品简介

芯天成静态时序分析工具EsseTime,是针对高可靠性场景下芯片时序分析的全新要求开发的产品,综合考虑老化效应以及工艺波动效应,协同EsseChar的老化库建模模块以及EsseSanity多工艺角性能分析优化功能,能够准确地分析和优化芯片关键路径的时序余量,为保证芯片设计功能正确性和稳定性提供强有力的支撑。

核心优势

灵活强大可靠性时序分析引擎;

实现近SPICE仿真级计算精度;

精确串扰噪声信号完整性分析;

多线程及分布式架构提升性能;

关键路径网表展示及交互查询;

多工具时序报告分析对比功能。

![]()

产品功能

支持CCS/NLDM模型;

支持各种不同偏差分析;

支持器件退化影响分析;

支持关键路径变化对比;

GUI界面信息查看对比;

标准化TCL命令结合图形操作。

应用方案

芯片设计时序签核检查;

车规芯片老化情况估算;

标准单元工艺波动影响;

辅助布局布线时序约束;

结合良率工具诊断分析。